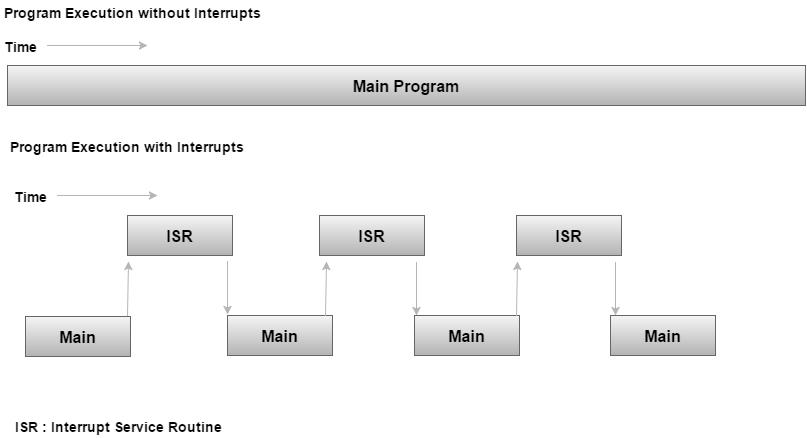

Un interrupt è un segnale al processore emesso da hardware o software che indica un evento che richiede attenzione immediata. Ogni volta che si verifica un interrupt, il controller completa l’esecuzione dell’istruzione corrente e inizia l’esecuzione di una Interrupt Service Routine (ISR) o Interrupt Handler. L’ISR dice al processore o al controller cosa fare quando si verifica l’interrupt. Gli interrupt possono essere sia hardware che software.

- Hardware Interrupt

- Interrupt software

- Che cos’è il polling?

- Interrupts v/s Polling

- Interrupt Service Routine

- Interrupt Vector Table

- Passi per eseguire un interrupt

- Edge Triggering vs. Level Triggering

- Abilitazione e disabilitazione di un interrupt

- Registro di abilitazione degli interrupt

- Priorità degli interrupt nell’8051

- Interrupt inside Interrupt

- Interrompere un interrupt via software

Hardware Interrupt

Un interrupt hardware è un segnale elettronico di avviso inviato al processore da un dispositivo esterno, come un controller di disco o una periferica esterna. Per esempio, quando premiamo un tasto sulla tastiera o muoviamo il mouse, si attivano degli interrupt hardware che fanno sì che il processore legga la pressione del tasto o la posizione del mouse.

Interrupt software

Un interrupt software è causato da una condizione eccezionale o da un’istruzione speciale nel set di istruzioni che causa un interrupt quando viene eseguita dal processore. Per esempio, se l’unità logica aritmetica del processore esegue un comando per dividere un numero per zero, per causare un’eccezione divide per zero, causando così che il computer abbandoni il calcolo o mostri un messaggio di errore. Le istruzioni di interruzione software funzionano in modo simile alle chiamate di subroutine.

Che cos’è il polling?

Lo stato di monitoraggio continuo è noto come polling. Il microcontrollore continua a controllare lo stato di altri dispositivi; e mentre lo fa, non fa altre operazioni e consuma tutto il suo tempo di elaborazione per il monitoraggio. Questo problema può essere affrontato usando gli interrupt.

Nel metodo dell’interrupt, il controller risponde solo quando si verifica un’interruzione. Così, il controllore non è tenuto a monitorare regolarmente lo stato (bandiere, segnali ecc.) dei dispositivi interfacciati e incorporati.

Interrupts v/s Polling

Ecco un’analogia che differenzia un interrupt dal polling –

| Interrupt | Polling |

|---|---|

| Un interrupt è come un negoziante. Se uno ha bisogno di un servizio o di un prodotto, va da lui e lo informa dei suoi bisogni. Nel caso degli interrupt, quando le bandiere o i segnali vengono ricevuti, essi notificano al controllore che hanno bisogno di essere serviti. | Il metodo del polling è come un venditore. Il venditore va di porta in porta chiedendo di comprare un prodotto o un servizio. Allo stesso modo, il controllore continua a monitorare le bandiere o i segnali uno per uno per tutti i dispositivi e fornisce il servizio a qualsiasi componente che ha bisogno del suo servizio. |

Interrupt Service Routine

Per ogni interrupt, ci deve essere un interrupt service routine (ISR), o gestore di interrupt. Quando si verifica un interrupt, il microcontrollore esegue l’interrupt service routine. Per ogni interrupt, c’è una posizione fissa in memoria che contiene l’indirizzo della sua interrupt service routine, ISR. La tabella delle locazioni di memoria messe da parte per tenere gli indirizzi degli ISR è chiamata Interrupt Vector Table.

Interrupt Vector Table

Ci sono sei interrupt incluso RESET nell’8051.

| Interruzioni | Localizzazione ROM (Hex) | Pin |

|---|---|---|

| Interruzioni | Localizzazione ROM (HEX) | |

| Com seriale (RI e TI) | 0023 | |

| Timer 1 interrupts(TF1) | 001B | |

| External HW interrupt 1 (INT1) | 0013 | P3.3 (13) |

| Interruzione HW esterna 0 (INT0) | 0003 | P3.2 (12) |

| Timer 0 (TF0) | 000B | |

| Reset | 0000 | 9 |

-

Quando il pin di reset viene attivato, l’8051 salta alla posizione di indirizzo 0000. Questo è il reset all’accensione.

-

Due interrupts sono impostati per i timer: uno per il timer 0 e uno per il timer 1. Le posizioni di memoria sono rispettivamente 000BH e 001BH nella tabella degli interrupt vector.

-

Due interrupt sono riservati agli interrupt hardware esterni. I pin 12 e 13 della porta 3 sono rispettivamente per gli interrupt hardware esterni INT0 e INT1. Le posizioni di memoria sono rispettivamente 0003H e 0013H nella tabella degli interrupt vector.

-

La comunicazione seriale ha un singolo interrupt che appartiene sia alla ricezione che alla trasmissione. La posizione di memoria 0023H appartiene a questo interrupt.

Passi per eseguire un interrupt

Quando un interrupt si attiva, il microcontrollore passa attraverso i seguenti passi –

-

Il microcontrollore chiude l’istruzione in esecuzione e salva l’indirizzo della prossima istruzione (PC) sullo stack.

-

Salva anche lo stato attuale di tutti gli interrupt internamente (cioè, non sullo stack).

-

Salta alla posizione di memoria della tabella degli interrupt vector che contiene l’indirizzo della routine di servizio degli interrupt.

-

Il microcontrollore ottiene l’indirizzo dell’ISR dalla tabella degli interrupt vector e vi salta. Inizia ad eseguire la subroutine di servizio d’interruzione, che è RETI (return from interrupt).

-

Eseguendo l’istruzione RETI, il microcontrollore ritorna alla posizione in cui è stato interrotto. Per prima cosa, ottiene l’indirizzo del contatore di programma (PC) dallo stack facendo un popping dei byte superiori dello stack nel PC. Poi, inizia l’esecuzione da quell’indirizzo.

Edge Triggering vs. Level Triggering

I moduli di interruzione sono di due tipi – level-triggered o edge-triggered.

| Level Triggered | Edge Triggered |

|---|---|

| Un modulo di interrupt a livello genera sempre un interrupt ogni volta che il livello della sorgente di interrupt è affermato. | Un modulo di interrupt edge-triggered genera un interrupt solo quando rileva un bordo affermato della sorgente di interrupt. Il bordo viene rilevato quando il livello della sorgente di interrupt cambia effettivamente. Può anche essere rilevato dal campionamento periodico e rilevare un livello asserito quando il campione precedente è stato de-asserito. |

| Se la sorgente di interrupt è ancora asserita quando il gestore di interrupt del firmware gestisce l’interrupt, il modulo di interrupt rigenererà l’interrupt, causando l’invocazione di nuovo del gestore di interrupt. | I moduli di interrupt edge-triggered possono essere agiti immediatamente, non importa come si comporta la sorgente di interrupt. |

| Gli interrupt attivati dal bordo sono ingombranti per il firmware. | Gli interrupt attivati dal bordo mantengono bassa la complessità del codice del firmware, riducono il numero di condizioni per il firmware e forniscono più flessibilità quando gli interrupt sono gestiti. |

Abilitazione e disabilitazione di un interrupt

Al reset, tutti gli interrupt sono disabilitati anche se sono attivati. Gli interrupt devono essere abilitati via software affinché il microcontrollore risponda a questi interrupt.

Il registro IE (interrupt enable) è responsabile dell’abilitazione e disabilitazione dell’interrupt. IE è un registro bit-indirizzabile.

Registro di abilitazione degli interrupt

| EA | – | ET2 | ES | ET1 | EX1 | ET0 | EX0 |

|---|

-

EA – Attiva/disattiva globale.

-

– – Non definito.

-

ET2 – Abilita l’interrupt del timer 2.

-

ES – Abilita l’interrupt della porta seriale.

-

ET1 – Abilita l’interrupt del timer 1.

-

EX1 – Abilita interrupt esterno 1.

-

ET0 – Abilita interrupt Timer 0.

-

EX0 – Abilita interrupt esterno 0.

Per abilitare un interrupt, facciamo i seguenti passi –

-

Il bit D7 del registro IE (EA) deve essere alto per permettere al resto del registro di avere effetto.

-

Se EA = 1, gli interrupt saranno abilitati e risponderanno, se i loro bit corrispondenti in IE sono alti. Se EA = 0, nessun interrupt risponderà, anche se i loro pin associati nel registro IE sono alti.

Priorità degli interrupt nell’8051

Possiamo modificare la priorità degli interrupt assegnando la priorità più alta a uno qualsiasi degli interrupt. Questo viene realizzato programmando un registro chiamato IP (priorità di interrupt).

La figura seguente mostra i bit del registro IP. Al reset, il registro IP contiene tutti 0. Per dare una priorità più alta a uno qualsiasi degli interrupt, rendiamo alto il bit corrispondente nel registro IP.

| – | – | – | PT1 | PX1 | PT0 | PX0 |

|---|

| – | IP.7 | Non implementato. |

| – | IP.6 | Non implementato. |

| – | IP.5 | Non implementato. |

| – | IP.4 | Non implementato. |

| PT1 | IP.3 | Definisce il livello di priorità dell’interrupt del Timer 1. |

| PX1 | IP.2 | Definisce il livello di priorità dell’interrupt esterno 1. |

| PT0 | IP.1 | Definisce il livello di priorità dell’interrupt del timer 0. |

| PX0 | IP.0 | Definisce il livello di priorità dell’Interrupt 0 esterno. |

Interrupt inside Interrupt

Cosa succede se l’8051 sta eseguendo un ISR che appartiene a un interrupt e un altro si attiva? In questi casi, un interrupt ad alta priorità può interrompere un interrupt a bassa priorità. Questo è noto come interrupt inside interrupt. In 8051, un interrupt a bassa priorità può essere interrotto da un interrupt ad alta priorità, ma non da un altro interrupt a bassa priorità.

Interrompere un interrupt via software

Ci sono momenti in cui abbiamo bisogno di testare un ISR tramite simulazione. Questo può essere fatto con le semplici istruzioni per impostare l’interrupt alto e quindi causare il salto dell’8051 alla tabella dei vettori di interrupt. Per esempio, impostate il bit IE a 1 per il timer 1. Un’istruzione SETB TF1 interromperà l’8051 in qualsiasi cosa stia facendo e lo costringerà a saltare alla tabella degli interrupt vector.

Lascia un commento