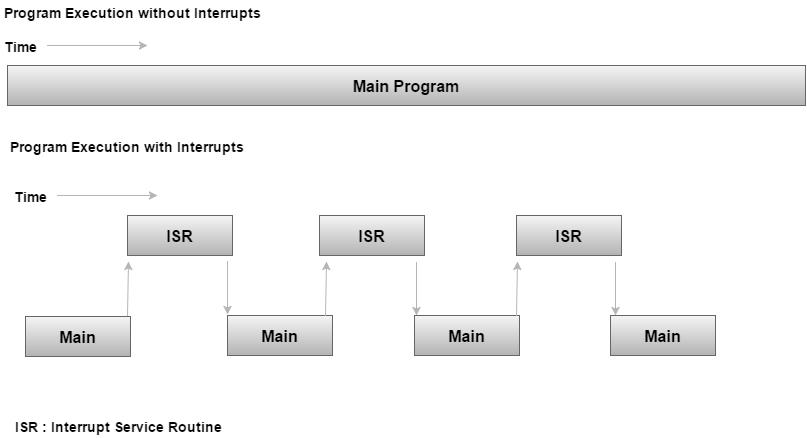

En avbrott är en signal till processorn som sänds ut av hårdvara eller mjukvara och som indikerar en händelse som kräver omedelbar uppmärksamhet. När ett avbrott inträffar avslutar styrenheten utförandet av den aktuella instruktionen och startar utförandet av en ISR (Interrupt Service Routine) eller Interrupt Handler (Interrupt Handler). ISR talar om för processorn eller styrenheten vad den ska göra när avbrottet inträffar. Avbrotten kan vara antingen hårdvaruavbrott eller mjukvaruavbrott.

- Hårdvaruavbrott

- Mjukvaruavbrott

- Vad är polling?

- Interrupts v/s Polling

- Interrupt Service Routine

- Interrupt Vector Table

- Steg för att utföra en interrupt

- Edge Triggering vs. Level Triggering

- Aktivering och inaktivering av ett avbrott

- Interrupt Enable Register

- Avbrottsprioritet i 8051

- Interrupt inside Interrupt

- Triggering an Interrupt by Software

Hårdvaruavbrott

Ett hårdvaruavbrott är en elektronisk varningssignal som sänds till processorn från en extern enhet, t.ex. en diskcontroller eller en extern perifer. När vi till exempel trycker på en tangent på tangentbordet eller flyttar musen utlöser de hårdvaruavbrott som gör att processorn läser av tangenttrycket eller musens position.

Mjukvaruavbrott

Ett mjukvaruavbrott orsakas antingen av ett undantagstillstånd eller av en särskild instruktion i instruktionsuppsättningen som orsakar ett avbrott när den exekveras av processorn. Om till exempel processorns aritmetiska logikenhet kör ett kommando för att dividera ett tal med noll, för att orsaka ett divide-by-zero-undantag, vilket gör att datorn avbryter beräkningen eller visar ett felmeddelande. Programvaruavbrottsinstruktioner fungerar på samma sätt som anrop av underprogram.

Vad är polling?

Det tillstånd av kontinuerlig övervakning kallas polling. Mikrokontrollern kontrollerar hela tiden statusen för andra enheter, och medan den gör det gör den ingen annan operation och använder all sin bearbetningstid till övervakning. Detta problem kan lösas genom att använda avbrott.

I avbrottsmetoden reagerar styrenheten endast när ett avbrott inträffar. Således behöver styrenheten inte regelbundet övervaka statusen (flaggor, signaler etc.) för interfacerade och inbyggda enheter.

Interrupts v/s Polling

Här är en analogi som skiljer ett interrupt från polling –

| Interrupt | Polling | |

|---|---|---|

| Ett interrupt är som en butiksinnehavare. Om någon behöver en tjänst eller produkt går han till honom och informerar honom om sina behov. När det gäller avbrott, när flaggorna eller signalerna tas emot, meddelar de kontrollanten att de måste servas. | Pollingmetoden är som en försäljare. Försäljaren går från dörr till dörr samtidigt som han ber om att få köpa en produkt eller tjänst. På samma sätt övervakar styrenheten flaggorna eller signalerna en efter en för alla enheter och ger service till den komponent som behöver sin service. |

Interrupt Service Routine

För varje avbrott måste det finnas en interrupt service rutin (ISR), eller interrupt handler. När ett avbrott inträffar kör mikrokontrollern avbrottsservicerutinen. För varje avbrott finns det en fast plats i minnet som innehåller adressen till dess avbrottsservicerutin, ISR. Tabellen med minnesplatser som är avsatta för att hålla adresserna till ISR:er kallas Interrupt Vector Table.

Interrupt Vector Table

Det finns sex avbrott inklusive RESET i 8051.

| Avbrott | ROM-plats (Hex) | Pin | |

|---|---|---|---|

| Avbrott | ROM-plats (HEX) | ||

| Serial COM (RI och TI) | 0023 | ||

| Timer 1-avbrott (TF1) | 001B | ||

| Externt HW-avbrott 1 (INT1) | 0013 | P3.3 (13) | |

| Externt HW-interrupt 0 (INT0) | 0003 | P3.2 (12) | |

| Timer 0 (TF0) | 000B | ||

| Reset | 0000 | 9 |

-

När nollställningsstiftet är aktiverat, hoppar 8051 till adressplatsen 0000. Detta är power-up reset.

-

Två avbrott är avsatta för timrarna: ett för timer 0 och ett för timer 1. Minnesplatserna är 000BH respektive 001BH i avbrottsvektortabellen.

-

Två avbrott är avsatta för externa avbrott för maskinvara. Stift nr 12 och stift nr 13 i port 3 är avsedda för de externa maskinvaruavbrotten INT0 respektive INT1. Minnesplatserna är 0003H respektive 0013H i avbrottsvektortabellen.

-

Seriekommunikation har ett enda avbrott som tillhör både mottagning och sändning. Minnesplats 0023H tillhör denna interrupt.

Steg för att utföra en interrupt

När en interrupt blir aktiv går mikrokontrollern igenom följande steg –

-

Mikrokontrollern stänger den för tillfället exekverade instruktionen och sparar adressen för nästa instruktion (PC) på stacken.

-

Den sparar också den aktuella statusen för alla avbrott internt (dvs, inte på stacken).

-

Den hoppar till den minnesplats i avbrottsvektortabellen som innehåller adressen till avbrottsservicerutinen.

-

Mikrokontrollern hämtar adressen till ISR från avbrottsvektortabellen och hoppar till den. Den börjar exekvera avbrottsserviceunderrutinen, som är RETI (return from interrupt).

-

När den exekverar RETI-instruktionen återvänder mikrokontrollern till den plats där den avbröts. Först hämtar den programräknarens (PC) adress från stapeln genom att ta upp de översta bytena från stapeln till PC. Sedan börjar den exekvera från den adressen.

Edge Triggering vs. Level Triggering

Interruptmoduler är av två typer – level-triggered eller edge-triggered.

| Nivåtriggad | Kanttriggad |

|---|---|

| En nivåtriggad avbrottsmodul genererar alltid ett avbrott när avbrottskällans nivå aktiveras. | En kanttriggad avbrottsmodul genererar ett avbrott endast när den upptäcker en aktiverad kant för avbrottskällan. Kanten upptäcks när avbrottskällans nivå faktiskt ändras. Den kan också upptäckas genom periodisk provtagning och genom att upptäcka en bekräftad nivå när föregående provtagning var avaktiverad. |

| Om avbrottskällan fortfarande är bekräftad när avbrottshanteraren i den inbyggda programvaran hanterar avbrottet, återskapar avbrottsmodulen avbrottet, vilket leder till att avbrottshanteraren åberopas på nytt. | Kanttriggerade avbrottsmoduler kan agera omedelbart, oavsett hur avbrottskällan beter sig. |

| Levelstiggade avbrott är besvärliga för firmware. | Edge-triggered interrupts håller den fasta programvarans kodkomplexitet låg, minskar antalet villkor för firmware och ger mer flexibilitet när avbrott hanteras. |

Aktivering och inaktivering av ett avbrott

Vid återställning inaktiveras alla avbrott även om de är aktiverade. Avbrotten måste aktiveras med hjälp av programvara för att mikrokontrollern ska kunna svara på dessa avbrott.

IE-registret (interrupt enable) är ansvarigt för att aktivera och inaktivera avbrottet. IE är ett bitadresserbart register.

Interrupt Enable Register

| EA | – | ET2 | ES | ET1 | EX1 | ET0 | EX0 |

|---|

-

EA – Global aktivering/avaktivering.

-

– – Odefinierad.

-

ET2 – Aktiverar avbrott för timer 2.

-

ES – Aktiverar avbrott för seriell port.

-

ET1 – Aktiverar avbrott för timer 1.

-

EX1 – Aktiverar externt 1 avbrott.

-

ET0 – Aktiverar timer 0 avbrott.

-

EX0 – Aktiverar externt 0 avbrott.

För att aktivera ett avbrott tar vi följande steg –

-

Bit D7 i IE-registret (EA) måste vara hög för att resten av registret ska få effekt.

-

Om EA = 1 aktiveras avbrott och besvaras, om deras motsvarande bits i IE är höga. Om EA = 0 kommer inga avbrott att svara, även om deras tillhörande bitar i IE-registret är höga.

Avbrottsprioritet i 8051

Vi kan ändra avbrottsprioriteten genom att tilldela högre prioritet till något av avbrotten. Detta görs genom att programmera ett register som kallas IP (interrupt priority).

Följande figur visar bitarna i IP-registret. Vid återställning innehåller IP-registret alla 0:or. För att ge högre prioritet åt något av avbrotten gör vi motsvarande bit i IP-registret hög.

| – | – | – | – | PT1 | PX1 | PT0 | PX0 |

|---|

| – | IP.7 | Inte genomfört. |

| – | IP.6 | Inte genomfört. |

| – | IP.5 | Inte genomfört. |

| – | IP.4 | Inte genomfört. |

| PT1 | IP.3 | Definierar prioritetsnivån för avbrottet Timer 1. |

| PX1 | IP.2 | Definierar prioritetsnivån för det externa avbrottet 1. |

| PT0 | IP.1 | Definierar prioritetsnivån för avbrottet Timer 0. |

| PX0 | IP.0 | Definierar prioritetsnivån för det externa avbrottet 0. |

Interrupt inside Interrupt

Vad händer om 8051 exekverar en ISR som hör till ett avbrott och ett annat blir aktivt? I sådana fall kan ett högprioriterat avbrott avbryta ett lågprioriterat avbrott. Detta kallas interrupt inside interrupt. I 8051 kan ett avbrott med låg prioritet avbrytas av ett avbrott med hög prioritet, men inte av något annat avbrott med låg prioritet.

Triggering an Interrupt by Software

Det finns tillfällen då vi behöver testa en ISR med hjälp av simulering. Detta kan göras med de enkla instruktionerna för att ställa in avbrottet högt och därmed få 8051 att hoppa till avbrottsvektortabellen. Sätt till exempel IE-biten till 1 för timer 1. En instruktion SETB TF1 kommer att avbryta 8051 i vad den än gör och tvinga den att hoppa till avbrottsvektortabellen.

Lämna ett svar