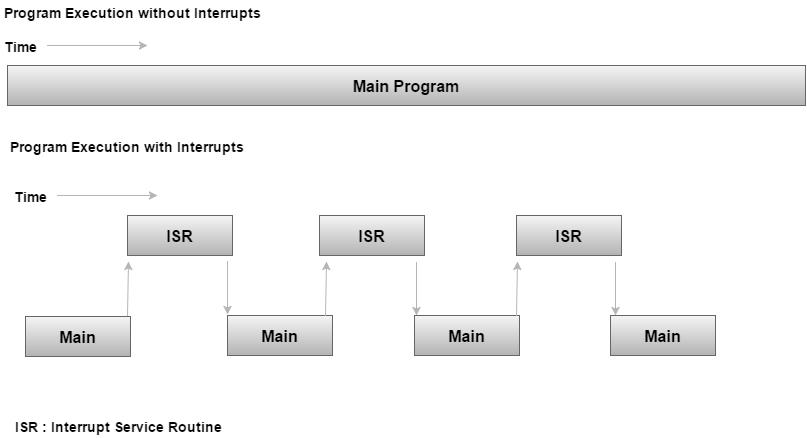

Una interrupción es una señal al procesador emitida por el hardware o el software que indica un evento que necesita atención inmediata. Cada vez que se produce una interrupción, el controlador finaliza la ejecución de la instrucción actual e inicia la ejecución de una Rutina de Servicio de Interrupción (ISR) o Manejador de Interrupción. La ISR indica al procesador o al controlador qué hacer cuando se produce la interrupción. Las interrupciones pueden ser de hardware o de software.

- Interrupción de hardware

- Interrupción de software

- ¿Qué es el sondeo?

- Interrupciones v/s Sondeo

- Rutina de servicio de interrupción

- Tabla de Vectores de Interrupción

- Pasos para ejecutar una interrupción

- Disparo por flanco vs. Disparo por nivel

- Habilitar y deshabilitar una interrupción

- Registro de habilitación de interrupción

- Prioridad de las interrupciones en el 8051

- Interrupción dentro de Interrupción

- Disparando una interrupción por software

Interrupción de hardware

Una interrupción de hardware es una señal electrónica de alerta enviada al procesador desde un dispositivo externo, como un controlador de disco o un periférico externo. Por ejemplo, cuando pulsamos una tecla del teclado o movemos el ratón, se desencadenan interrupciones de hardware que hacen que el procesador lea la pulsación de la tecla o la posición del ratón.

Interrupción de software

Una interrupción de software está causada por una condición excepcional o por una instrucción especial del conjunto de instrucciones que provoca una interrupción cuando es ejecutada por el procesador. Por ejemplo, si la unidad aritmética lógica del procesador ejecuta una instrucción para dividir un número por cero, para provocar una excepción de división por cero, haciendo así que el ordenador abandone el cálculo o muestre un mensaje de error. Las instrucciones de interrupción de software funcionan de forma similar a las llamadas a subrutinas.

¿Qué es el sondeo?

El estado de monitorización continua se conoce como sondeo. El microcontrolador sigue comprobando el estado de otros dispositivos; y mientras lo hace, no realiza ninguna otra operación y consume todo su tiempo de procesamiento para la monitorización. Este problema puede solucionarse utilizando interrupciones.

En el método de las interrupciones, el controlador responde sólo cuando se produce una interrupción. Por lo tanto, el controlador no necesita supervisar regularmente el estado (banderas, señales, etc.) de los dispositivos interconectados e incorporados.

Interrupciones v/s Sondeo

Aquí hay una analogía que diferencia una interrupción del sondeo –

| Interrupción | Sondeo |

|---|---|

| Una interrupción es como un tendero. Si uno necesita un servicio o un producto, acude a él y le informa de sus necesidades. En el caso de las interrupciones, cuando se reciben las banderas o señales, notifican al controlador que necesitan un servicio. | El método de sondeo es como un vendedor. El vendedor va de puerta en puerta solicitando la compra de un producto o servicio. Del mismo modo, el controlador sigue monitoreando las banderas o señales una por una para todos los dispositivos y proporciona servicio a cualquier componente que necesite su servicio. |

Rutina de servicio de interrupción

Para cada interrupción, debe haber una rutina de servicio de interrupción (ISR), o controlador de interrupción. Cuando se produce una interrupción, el microcontrolador ejecuta la rutina de servicio de interrupción. Para cada interrupción, hay una ubicación fija en la memoria que contiene la dirección de su rutina de servicio de interrupción, ISR. La tabla de ubicaciones de memoria reservada para mantener las direcciones de ISR se llama Tabla de Vectores de Interrupción.

Tabla de Vectores de Interrupción

Hay seis interrupciones incluyendo RESET en el 8051.

| Interrupciones | Localización de la ROM (Hex) | Pin |

|---|---|---|

| Interrupciones | Localización de la ROM (HEX) | |

| Serial COM (RI y TI) | 0023 | |

| Interrupciones del temporizador 1(TF1) | 001B | |

| Interrupción HW externa 1 (INT1) | 0013 | P3.3 (13) |

| Interrupción HW externa 0 (INT0) | 0003 | P3.2 (12) |

| Temporizador 0 (TF0) | 000B | |

| Reset | 0000 | 9 |

-

Cuando se activa el pin de reset, el 8051 salta a la dirección 0000. Esto es el reinicio de encendido.

-

Dos interrupciones se reservan para los temporizadores: una para el temporizador 0 y otra para el temporizador 1. Las posiciones de memoria son 000BH y 001BH respectivamente en la tabla de vectores de interrupción.

-

Dos interrupciones se reservan para las interrupciones externas de hardware. El pin nº 12 y el pin nº 13 del puerto 3 son para las interrupciones hardware externas INT0 e INT1, respectivamente. Las posiciones de memoria son 0003H y 0013H respectivamente en la tabla de vectores de interrupción.

-

La comunicación serial tiene una sola interrupción que pertenece tanto a la recepción como a la transmisión. La posición de memoria 0023H pertenece a esta interrupción.

Pasos para ejecutar una interrupción

Cuando una interrupción se activa, el microcontrolador pasa por los siguientes pasos –

-

El microcontrolador cierra la instrucción que se está ejecutando y guarda la dirección de la siguiente instrucción (PC) en la pila.

-

También guarda el estado actual de todas las interrupciones internamente (es decir, no en la pila).

-

Salta a la posición de memoria de la tabla de vectores de interrupción que contiene la dirección de la rutina de servicio de interrupción.

-

El microcontrolador obtiene la dirección de la ISR de la tabla de vectores de interrupción y salta a ella. Comienza a ejecutar la subrutina de servicio de interrupción, que es RETI (return from interrupt).

-

Al ejecutar la instrucción RETI, el microcontrolador vuelve a la ubicación donde fue interrumpido. En primer lugar, obtiene la dirección del contador de programa (PC) de la pila haciendo saltar los bytes superiores de la pila en el PC. Luego, comienza a ejecutarse desde esa dirección.

Disparo por flanco vs. Disparo por nivel

Los módulos de interrupción son de dos tipos -disparo por nivel o por flanco.

| Disparado por nivel | Disparado por flanco |

|---|---|

| Un módulo de interrupción disparado por nivel siempre genera una interrupción cuando se afirma el nivel de la fuente de interrupción. | Un módulo de interrupción disparado por flanco genera una interrupción sólo cuando detecta un flanco de afirmación de la fuente de interrupción. El flanco se detecta cuando el nivel de la fuente de interrupción cambia realmente. También puede detectarse mediante el muestreo periódico y la detección de un nivel asertivo cuando el muestreo anterior fue desasertivo. |

| Si la fuente de interrupción sigue asertiva cuando el manejador de interrupción del firmware maneja la interrupción, el módulo de interrupción regenerará la interrupción, haciendo que el manejador de interrupción sea invocado de nuevo. | Los módulos de interrupción activados por flanco pueden actuar inmediatamente, sin importar el comportamiento de la fuente de interrupción. |

| Las interrupciones activadas por el borde son engorrosas para el firmware. | Las interrupciones activadas por el borde mantienen baja la complejidad del código del firmware, reducen el número de condiciones para el firmware y proporcionan más flexibilidad cuando se manejan las interrupciones. |

Habilitar y deshabilitar una interrupción

Al reiniciar, todas las interrupciones se deshabilitan aunque estén activadas. Las interrupciones deben habilitarse por software para que el microcontrolador responda a dichas interrupciones.

El registro IE (interrupt enable) se encarga de habilitar y deshabilitar la interrupción. IE es un registro direccionable por bits.

Registro de habilitación de interrupción

| EA | – | ET2 | ES | ET1 | EX1 | ET0 |

|---|

-

EA – Habilitación/deshabilitación global.

-

– – Indefinido.

-

ET2 – Habilita la interrupción del temporizador 2.

-

ES – Habilita la interrupción del puerto serie.

-

ET1 – Habilita la interrupción del temporizador 1.

-

EX1 – Habilita la interrupción externa 1.

-

ET0 – Habilita la interrupción del temporizador 0.

-

EX0 – Habilita la interrupción externa 0.

Para habilitar una interrupción, seguimos los siguientes pasos –

-

El bit D7 del registro IE (EA) debe estar alto para que el resto del registro tenga efecto.

-

Si EA = 1, se habilitarán las interrupciones y se responderá a ellas, si sus bits correspondientes en IE están altos. Si EA = 0, ninguna interrupción responderá, aunque sus bits asociados en el registro IE estén altos.

Prioridad de las interrupciones en el 8051

Podemos alterar la prioridad de las interrupciones asignando la mayor prioridad a cualquiera de ellas. Esto se consigue programando un registro llamado IP (interrupt priority).

La siguiente figura muestra los bits del registro IP. Al reiniciar, el registro IP contiene todos 0’s. Para dar una mayor prioridad a alguna de las interrupciones, hacemos que el bit correspondiente del registro IP sea alto.

| – | – | – | – | PX1 | PT0 | PX0 |

|---|

| – | IP.7 | Sin implementar. |

| – | IP.6 | Sin implementar. |

| – | IP.5 | Sin implementar. |

| – | IP.4 | Sin implementar. |

| PT1 | IP.3 | Define el nivel de prioridad de la interrupción del temporizador 1. |

| PX1 | IP.2 | Define el nivel de prioridad de la interrupción externa 1. |

| PT0 | IP.1 | Define el nivel de prioridad de la interrupción del temporizador 0. |

| PX0 | IP.0 | Define el nivel de prioridad de la interrupción externa 0. |

Interrupción dentro de Interrupción

¿Qué ocurre si el 8051 está ejecutando un ISR que pertenece a una interrupción y se activa otra? En estos casos, una interrupción de alta prioridad puede interrumpir una interrupción de baja prioridad. Esto se conoce como interrupción dentro de la interrupción. En el 8051, una interrupción de baja prioridad puede ser interrumpida por una interrupción de alta prioridad, pero no por otra interrupción de baja prioridad.

Disparando una interrupción por software

Hay veces que necesitamos probar un ISR por medio de la simulación. Esto se puede hacer con las simples instrucciones para poner la interrupción en alto y así hacer que el 8051 salte a la tabla de vectores de interrupción. Por ejemplo, establezca el bit IE como 1 para el temporizador 1. Una instrucción SETB TF1 interrumpirá al 8051 en lo que esté haciendo y lo obligará a saltar a la tabla de vectores de interrupción.

Deja una respuesta