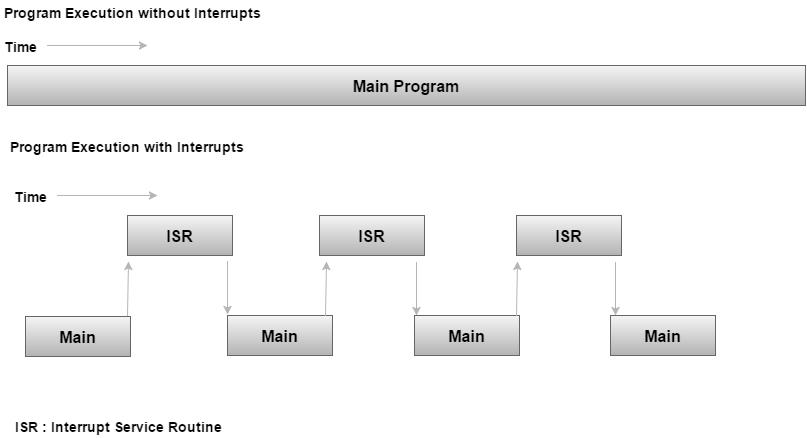

En afbrydelse er et signal til processoren, der udsendes af hardware eller software, og som indikerer en hændelse, der kræver øjeblikkelig opmærksomhed. Når der opstår en afbrydelse, afslutter controlleren udførelsen af den aktuelle instruktion og starter udførelsen af en Interrupt Service Routine (ISR) eller Interrupt Handler (Interrupt Handler). ISR fortæller processoren eller controlleren, hvad den skal gøre, når afbrydelsen opstår. Afbrydelserne kan enten være hardwareinterrupts eller softwareinterrupts.

- Hardwareinterrupt

- Softwareinterrupt

- Hvad er polling?

- Interrupts v/s Polling

- Interrupt Service Routine

- Interrupt Vector Table

- Stræk til udførelse af en interrupt

- Edge Triggering vs. Level Triggering

- Aktivering og deaktivering af en afbrydelse

- Interrupt Enable Register

- Interruptprioritet i 8051

- Interrupt inside Interrupt

- Triggering af en interrupt ved hjælp af software

Hardwareinterrupt

En hardwareinterrupt er et elektronisk advarselssignal, der sendes til processoren fra en ekstern enhed, f.eks. en diskcontroller eller et eksternt periferiudstyr. Når vi f.eks. trykker på en tast på tastaturet eller bevæger musen, udløser de hardwareinterrupts, som får processoren til at aflæse tastetrykket eller musens position.

Softwareinterrupt

Et softwareinterrupt skyldes enten en ekstraordinær tilstand eller en særlig instruktion i instruktionssættet, som udløser et interrupt, når den udføres af processoren. Hvis processorens aritmetiske logikenhed f.eks. kører en kommando om at dividere et tal med nul, for at forårsage en divide-by-nul-undtagelse, hvilket får computeren til at opgive beregningen eller vise en fejlmeddelelse. Softwareafbrydelsesinstruktioner fungerer på samme måde som underprogramopkald.

Hvad er polling?

Den tilstand, hvor der foregår løbende overvågning, kaldes polling. Mikrocontrolleren kontrollerer hele tiden status for andre enheder; og mens den gør det, udfører den ingen andre operationer og bruger al sin behandlingstid på overvågning. Dette problem kan løses ved at bruge afbrydelser.

I afbrydelsesmetoden reagerer controlleren kun, når der opstår en afbrydelse. Det er således ikke nødvendigt, at controlleren regelmæssigt overvåger status (flag, signaler osv.) for interfaced og indbyggede enheder.

Interrupts v/s Polling

Her er en analogi, der adskiller en interrupt fra polling –

| Interrupt | Polling | |

|---|---|---|

| En interrupt er som en butiksindehaver. Hvis man har brug for en tjeneste eller et produkt, går man hen til ham og informerer ham om sine behov. I tilfælde af interrupts meddeler de, når flagene eller signalerne modtages, controlleren, at de skal serviceres. | Polling-metoden er som en sælger. Sælgeren går fra dør til dør, mens han anmoder om at købe et produkt eller en tjenesteydelse. På samme måde holder controlleren øje med flagene eller signalerne en efter en for alle enheder og yder service til den komponent, der har brug for sin service. |

Interrupt Service Routine

For hver afbrydelse skal der være en interrupt service rutine (ISR), eller interrupt handler. Når der opstår en afbrydelse, kører mikrocontrolleren afbrydelsesservicerutinen. For hver afbrydelse er der et fast sted i hukommelsen, som indeholder adressen på dens afbrydelsesservicerutine, ISR. Tabellen over hukommelsesplaceringer, der er afsat til at indeholde adresserne for ISR’er, kaldes Interrupt Vector Table.

Interrupt Vector Table

Der er seks interrupts, herunder RESET, i 8051.

| Interrupts | ROM-placering (Hex) | Pin | |

|---|---|---|---|

| Interrupts | ROM-placering (HEX) | ||

| Seriel COM (RI og TI) | 0023 | ||

| Timer 1 interrupts(TF1) | 001B | ||

| External HW interrupt 1 (INT1) | 0013 | P3.3 (13) | |

| Ekstern HW-interrupt 0 (INT0) | 0003 | P3.2 (12) | |

| Timer 0 (TF0) | 000B | ||

| Reset | 0000 | 9 |

-

Når reset-pinden er aktiveret, hopper 8051’eren til adresseplacering 0000. Dette er power-up reset.

-

Der er afsat to interrupts til timerne: en til timer 0 og en til timer 1. Hukommelsesplaceringerne er henholdsvis 000BH og 001BH i interruptvektortabellen.

-

To interrupts er afsat til eksterne hardware-interrupts. Pin nr. 12 og Pin nr. 13 i port 3 er til henholdsvis de eksterne hardwareinterrupts INT0 og INT1. Hukommelsesplaceringerne er henholdsvis 0003H og 0013H i interruptvektortabellen.

-

Seriel kommunikation har en enkelt interrupt, der hører til både modtagelse og transmission. Hukommelsesplacering 0023H hører til denne interrupt.

Stræk til udførelse af en interrupt

Når en interrupt bliver aktiv, gennemgår mikrocontrolleren følgende trin –

-

Mikrocontrolleren afslutter den aktuelt udførte instruktion og gemmer adressen på den næste instruktion (PC) på stakken.

-

Den gemmer også den aktuelle status for alle afbrydelser internt (dvs, ikke på stakken).

-

Den hopper til den hukommelsesplacering i afbrydelsesvektortabellen, der indeholder adressen på interruptservicerutinen.

-

Mikrocontrolleren henter adressen på ISR’en fra afbrydelsesvektortabellen og hopper til den. Den begynder at udføre interrupt service subroutinen, som er RETI (return from interrupt).

-

Når den udfører RETI-instruktionen, vender mikrocontrolleren tilbage til det sted, hvor den blev afbrudt. Først henter den adressen på programtælleren (PC) fra stakken ved at poppe de øverste bytes af stakken ind i PC’en. Derefter begynder den at udføre fra denne adresse.

Edge Triggering vs. Level Triggering

Interruptmoduler er af to typer – level-triggered eller edge-triggered.

| Level Triggered | Edge Triggered |

|---|---|

| Et level-triggered afbrydelsesmodul genererer altid en afbrydelse, når niveauet for afbrydelseskilden er aktiveret. | Et edge-triggered afbrydelsesmodul genererer kun en afbrydelse, når det registrerer en aktiveret flanke af afbrydelseskilden. Flanken bliver registreret, når afbrydelseskildens niveau faktisk ændres. Den kan også detekteres ved periodisk prøvetagning og detektering af et bekræftet niveau, når den foregående prøve blev de-aktiveret. |

| Hvis afbrydelseskilden stadig er bekræftet, når firmwarens afbrydelseshåndtering håndterer afbrydelsen, vil afbrydelsesmodulet regenerere afbrydelsen, hvilket får afbrydelseshåndteringen til at blive påberåbt igen. | Edge-triggered afbrydelsesmoduler kan handles med det samme, uanset hvordan afbrydelseskilden opfører sig. |

| Level-triggered interrupts er besværlige for firmware. | Edge-triggered interrupts holder firmwarens kodekompleksitet lav, reducerer antallet af betingelser for firmware og giver mere fleksibilitet, når interrupts håndteres. |

Aktivering og deaktivering af en afbrydelse

Ved nulstilling er alle afbrydelser deaktiveret, selv om de er aktiveret. Afbrydelserne skal aktiveres ved hjælp af software, for at mikrocontrolleren kan reagere på disse afbrydelser.

IE-registret (interrupt enable) er ansvarligt for at aktivere og deaktivere afbrydelsen. IE er et register, der kan bitadresseres.

Interrupt Enable Register

| EA | – | ET2 | ES | ET1 | EX1 | ET0 | EX0 |

|---|

-

EA – Global aktivering/ deaktivering.

-

– – Udefineret.

-

ET2 – Aktiverer afbrydelse af Timer 2.

-

ES – Aktiverer afbrydelse af seriel port.

-

ET1 – Aktiverer afbrydelse af Timer 1.

-

EX1 – Aktiverer ekstern 1 afbrydelse.

-

ET0 – Aktiverer Timer 0 afbrydelse.

-

EX0 – Aktiverer ekstern 0 afbrydelse.

For at aktivere en afbrydelse tager vi følgende skridt –

-

Bit D7 i IE-registret (EA) skal være høj, for at resten af registret kan få effekt.

-

Hvis EA = 1, vil afbrydelser blive aktiveret og reageres på, hvis deres tilsvarende bits i IE er høje. Hvis EA = 0, vil ingen afbrydelser reagere, selv om deres tilhørende pins i IE-registeret er høje.

Interruptprioritet i 8051

Vi kan ændre interruptprioriteten ved at tildele den højere prioritet til en af afbrydelserne. Dette gøres ved at programmere et register kaldet IP (interruptprioritet).

Den følgende figur viser bittene i IP-registret. Ved nulstilling indeholder IP-registeret alle 0’er. For at give en højere prioritet til en af afbrydelserne sætter vi den tilsvarende bit i IP-registeret højt.

| – | – | – | – | PT1 | PX1 | PT0 | PX0 |

|---|

| – | IP.7 | ikke implementeret. | |

| – | IP.6 | ikke implementeret. | |

| – | IP.5 | Ikke implementeret. | |

| – | – | IP.4 | Ikke implementeret. |

| PT1 | IP.3 | Definerer prioritetsniveauet for afbrydelse af Timer 1. | |

| PX1 | IP.2 | Definerer prioritetsniveauet for ekstern afbrydelse 1. | |

| PT0 | IP.1 | Definerer prioritetsniveauet for afbrydelse af Timer 0. | |

| PX0 | IP.0 | Definerer prioritetsniveauet for ekstern interrupt 0. |

Interrupt inside Interrupt

Hvad sker der, hvis 8051 er ved at udføre en ISR, der hører til en interrupt, og en anden bliver aktiv? I sådanne tilfælde kan en højprioritetsinterrupt afbryde en lavprioritetsinterrupt. Dette er kendt som interrupt inside interrupt. I 8051 kan en interrupt med lav prioritet afbrydes af en interrupt med høj prioritet, men ikke af en anden interrupt med lav prioritet.

Triggering af en interrupt ved hjælp af software

Der er tidspunkter, hvor vi har brug for at teste en ISR ved hjælp af simulering. Dette kan gøres med de enkle instruktioner til at sætte interruptet højt og derved få 8051 til at springe til interrupt-vektortabellen. Sæt f.eks. IE-bitten som 1 for timer 1. En instruktion SETB TF1 vil afbryde 8051’eren i det, den er i gang med, og tvinge den til at springe til afbrydelsesvektortabellen.

Skriv et svar